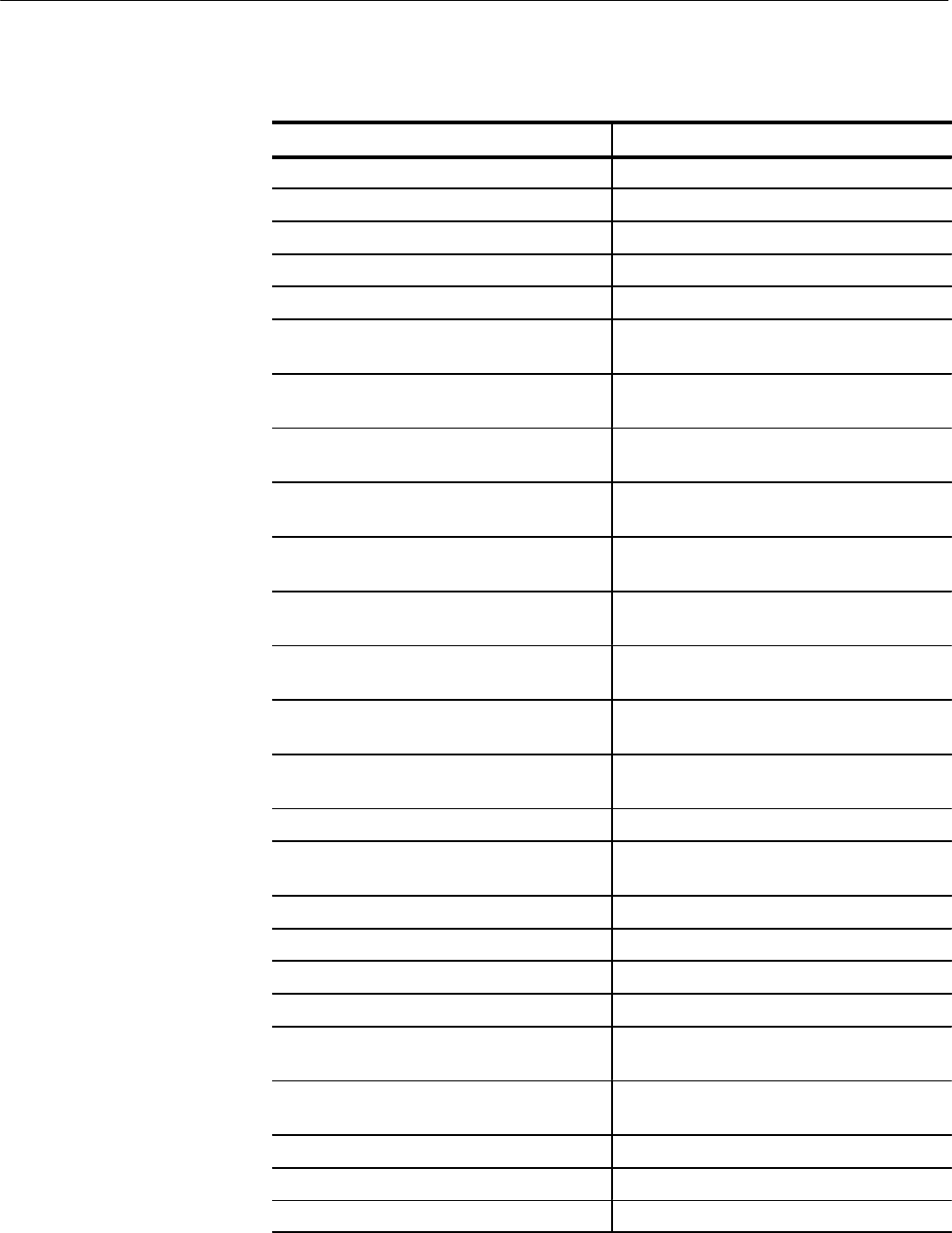

Appendix D: Factory Initialization Settings

TLS 216 Programmer Manual

D–3

Table D–1: Factory Initialization Defaults (Cont.)

Control Changed by Factory Init to

Measure Low Ref 10% and 0 V (units)

Measure Mid Ref 50% and 0 V (units)

Measure Mid2 Ref 50% and 0 V (units)

Measure Setup or Hold Clock Source Channel 1 (Ch1)

Measure Setup or Hold Clock Edge Rising and forward searching

Pattern, Sequence, and State trigger patterns

(Main and Delayed)

Ch 1 = H (HIGH); all others = X (don’t care)

Pattern and Sequence trigger

time qualification type (Main and Delayed)

Time Limit

Pattern and Sequence trigger time qualifier,

time-limit qualified (Main and Delayed)

TRUE for > Time

Pattern and Sequence trigger time setting,

time-limit qualified (Main and Delayed)

2.0 ns

Pattern and Sequence trigger upper limit time,

time-range qualified (Main and Delayed)

2.0 ns

Pattern and Sequence trigger lower limit time,

time-range qualified (Main and Delayed)

2.0 ns

Pattern and Sequence trigger time qualifier,

time range qualified (Main and Delayed)

In Range

Pattern, Sequence, and State trigger logic

definition

AND

Pattern, Sequence, and State trigger thresh-

olds (Main and Delayed)

Channels 1-16 = 0V; AUX = 1.5 V

Pulse glitch trigger polarity (Main and Delayed) Positive

Pulse glitch trigger when ... (Main and

Delayed)

True < Time

Pulse trigger class (Main and Delayed) Glitch

Pulse trigger glitch width (Main and Delayed) 2.0 ns

Pulse trigger glitch width (Main and Delayed) Upper limit = 2.0 ns

Pulse trigger threshold (Main and Delayed) 0.0 V

Pulse trigger source — Glitch and width (Main

and Delayed)

Channel 1 (Ch1)

Pulse width trigger when ... (Main and

Delayed)

Within limits

Pulse width upper limit (Main and Delayed) 2.0 ns

Pulse width lower limit (Main and Delayed) 2.0 ns

Pulse width trigger polarity (Main and Delayed) Positive