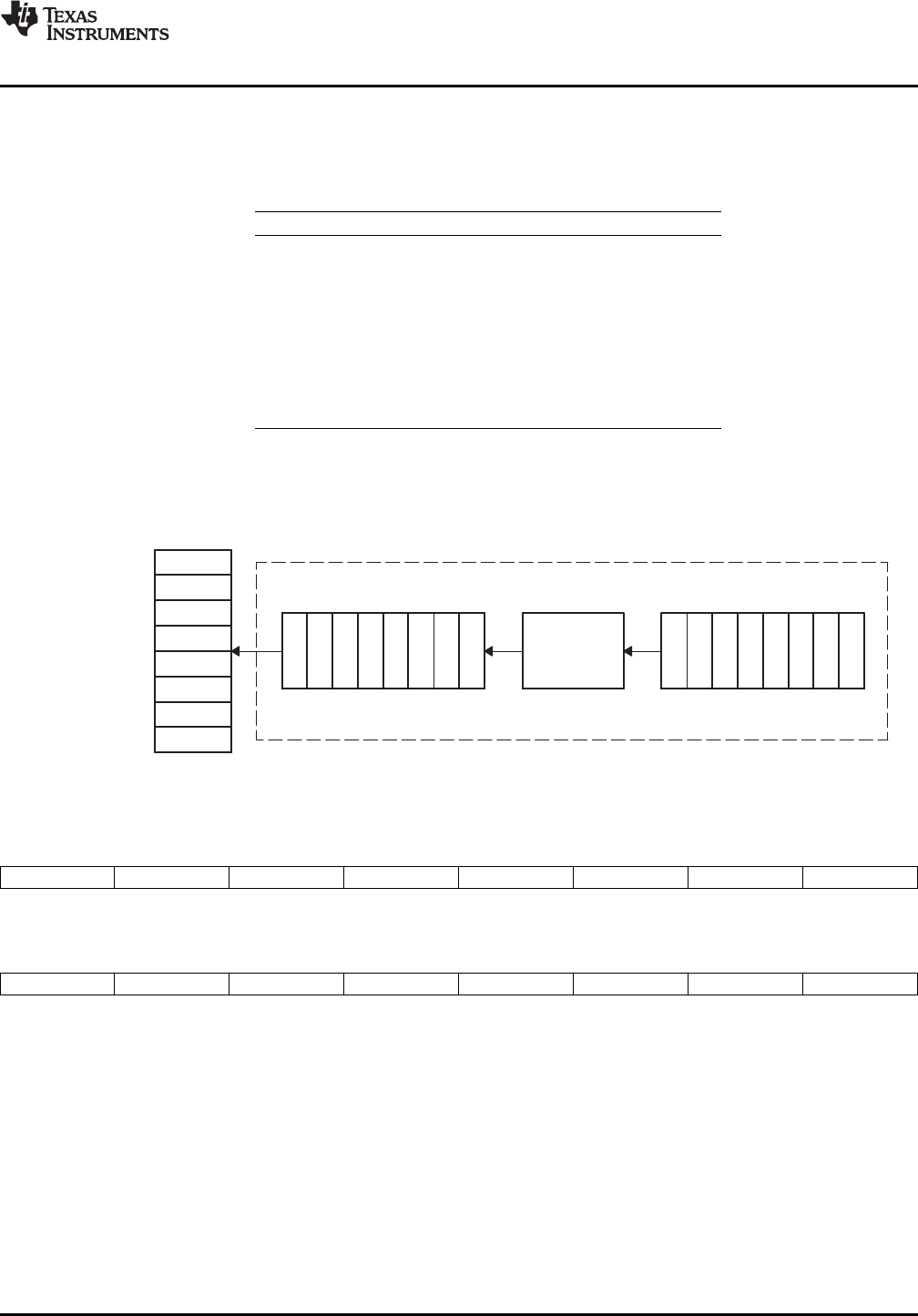

7.1.4.2ENDIAN_EXTR=0

XT3

XT2

XT1

XT0

XT7

XT5

XT4

XT6

Base 0

Base 7

Endian_Extr=0

XT7

XT6

XT5

XT4

XT0

XT2

XT3

XT1

Endianness

manager

XT7

XT6

XT5

XT4

XT3

XT2

XT1

XT0

63 0 63 0

EDMA3

TCP

Kernel

Memory

8Architecture

www.ti.com

Architecture

IfENDIAN_EXTR=0,dataaresavedinwordformat(32bits)intheDSP(seeTable39).

Table39.ExtrinsicinDSPMemory(ENDIAN_EXTR=

0)

Address(hexbytes)Data

BaseEXT3

Base+1EXT2

Base+2EXT1

Base+3EXT0

Base+4EXT7

Base+5EXT6

Base+6EXT5

Base+7EXT4

Figure92.ExtrinsicinDSPMemory(ENDIAN_EXTR=0)

TheyhavetobeswappedasdescribedinFigure93andFigure94.

Figure93.DataSource-Kernel(ENDIAN_EXTR=0)

63:5655:4847:4039:3231:2423:1615:87:0

EXT7EXT6EXT5EXT4EXT3EXT2EXT1EXT0

Figure94.DataDestination-EDMA3(ENDIAN_EXTR=0)

63:5655:4847:4039:3231:2423:1615:87:0

EXT3EXT2EXT1EXT0EXT7EXT6EXT5EXT4

TheTCP2processingunit(MAPunit)isshowninFigure95.ThebetakernelperformstheMAPalgorithm

backwardrecursionandproducesbetaprobabilitiesstoredinthebetaRAM.Thealphakernelperforms

theforwardrecursionproducingalphaprobabilities,andtheextrinsicblockcomputestheextrinsicstobe

storedintheextrinsicsmemory.

TheprocessingunitimplementstheMax*Log-MAPalgorithmusingaslidingwindowtechniquethatallows

parallelprocessingandreducesdramaticmemoryrequirements.

SPRUGK1–March2009TMS320C6457Turbo-DecoderCoprocessor259

SubmitDocumentationFeedback