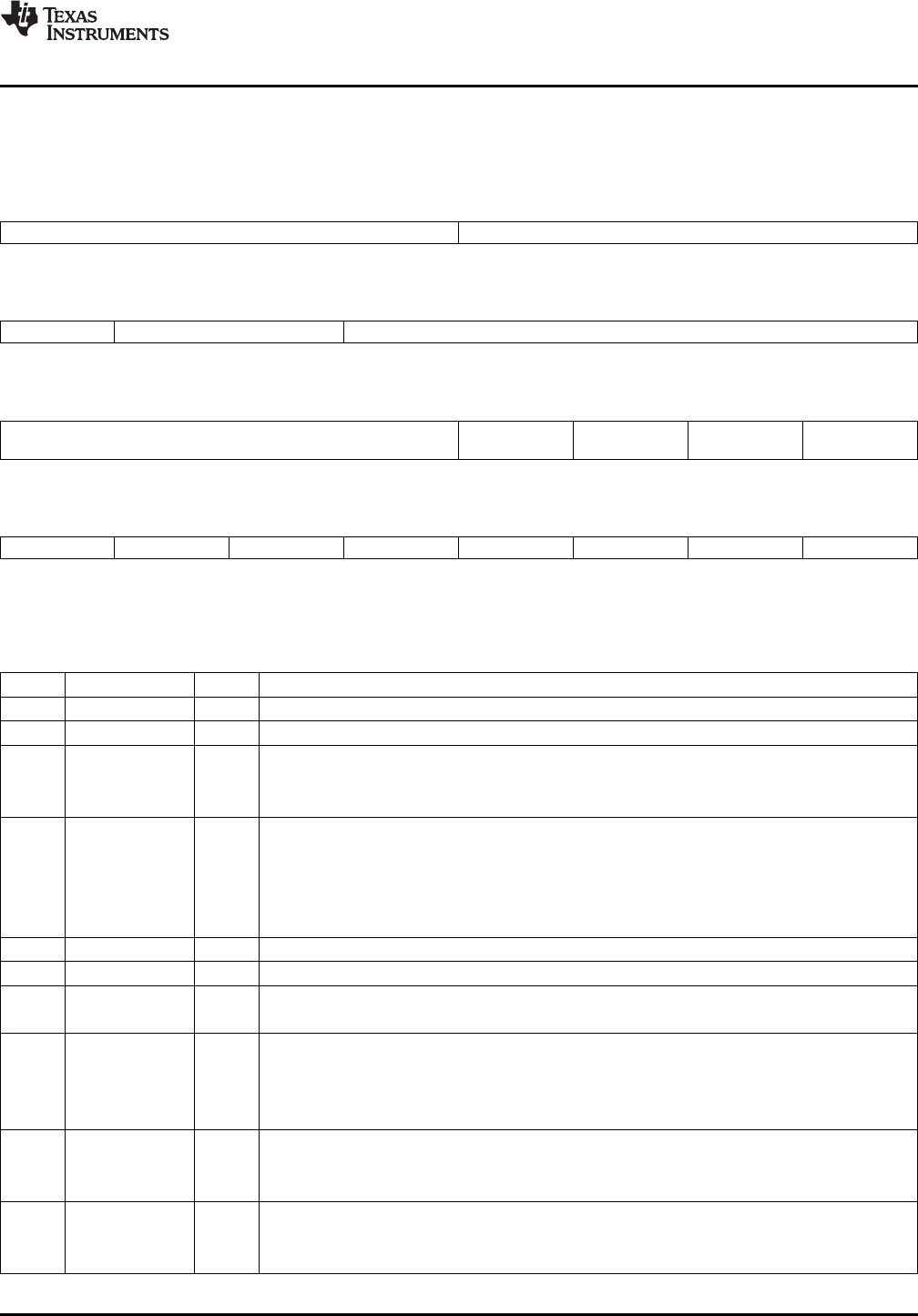

6.25TCP2StatusRegister(TCPSTAT)

www.ti.com

Registers

TheTCP2statusregister(TCPSTAT)isshowninFigure55anddescribedinTable30.

Figure55.TCP2StatusRegister(TCPSTAT)

31282724

ReservedTCP_STATE

R-0R-0

2322212016

CRC_PASSSNR_EXCEEDACTIVE_ITER

R-0R-0R-0

1512111098

ACTIVE_

ACTIVE_STATEEMUHALTROPRHD

MAP

R-0R-0R-0R-0R-0

76543210

REXTWAPWSPWINTWICERRDEC_BUSYReserved

R-0R-0R-0R-0R-0R-0R-0R-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table30.TCP2StatusRegister(TCPSTAT)FieldDescriptions

BitFieldValueDescription

31-28Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

27-24TCP_STATETCP2toplevelstateofstatemachine.ThestatesaredefinedintheTCP2statemachinesection.

23CRC_PASSCRCstatus

0CRChasnotpassed

1CRCpassed

22-21SNR_EXCEEDSNRstatus

00MAP0failedSNR

01MAP0passedSNR

10MAP1failedSNR

11MAP1passedSNR

20-16ACTIVE_ITERActiveTCP2iterationstatus.

15-12ACTIVE_STATEActivestatestatus

11ACTIVE_MAPActivemapstatus

Note:ACTIVE_MAPbitstatusisreservedwhentheFREEbit=0andtheSOFTbit=0.

10EMUHALTDefinesiftheTCP2ishaltedduetoemulation.

0Nothaltedduetoemulation

1Haltedduetoemulation

Note:EMUHALTbitstatusisreservedwhentheFREEbit=0andtheSOFTbit=1.

9ROPDefinesiftheTCP2iswaitingforoutputparameterdatatoberead.

0Notwaiting

1WaitingforRAMoutputregisterstoberead

8RHDDefinesiftheTCP2iswaitingforharddecisiondatatoberead.

0Notwaiting

1WaitingforRAMoutput/decisionmemorytoberead

SPRUGK1–March2009TMS320C6457Turbo-DecoderCoprocessor247

SubmitDocumentationFeedback