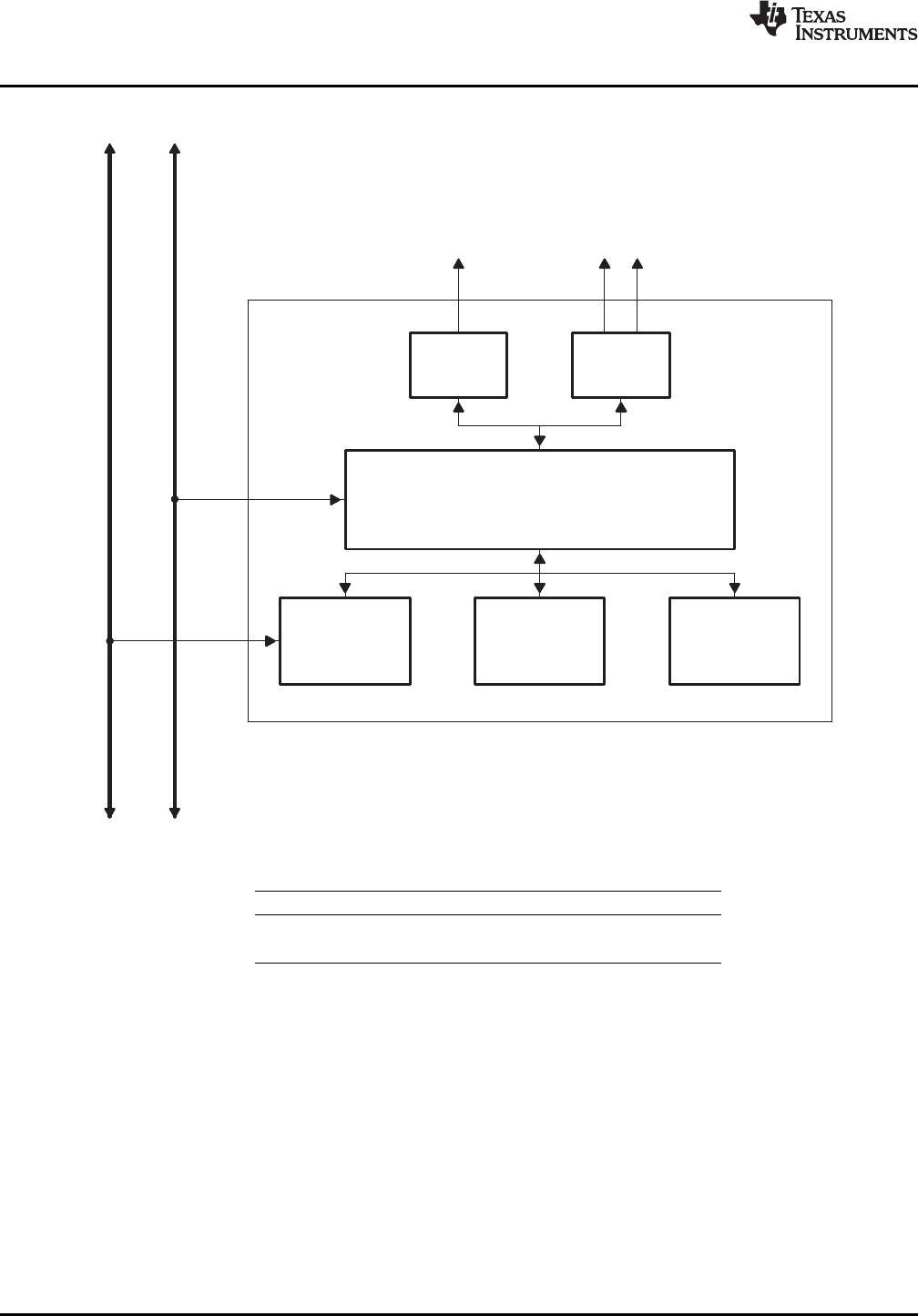

32-bit configuration bus

64-bit EDMA3 bus

Turbo-decoder coprocessor (TCP2)

REVT/XEVT

generation

CPU

interrupt

generation

TCP2 control

EDMA3 I/F unit Memory block Processing unit

TCP2_INT TCPXEVT TCPREVT

4Standalone(SA)Mode

Standalone(SA)Mode

www.ti.com

Figure3.TCP2BlockDiagram

Table1.FrameSizesforStandalone(SA)Modeand

Shared-Processing(SP)Mode

FrameSize(F)TCP2Mode

40⇐F⇐20730Standalonemode

F>20730Sharedprocessing

Instandalone(SA)mode,theDSPsendsthesystematicandparitydata,andtheinterleavertable.The

TCP2thenworksindependentlyoftheDSP(standalone),iteratesadefinedmaximumnumberoftimes,

andoutputsharddecisiondata.Inthismode,minimumDSPprocessingisrequired.Astoppingcriteria

canbeenabledtoreducetheprocessingdelay(seeSection4.3).Figure4showstheSAmode.

Thestandalonemodeisusedforframesinwhichtheturbointerleaverlengthislessthanorequalto

20730.Inthismode,thesystematic,parities,extrinsics,andturbointerleaverdatafitwithintheTCP2

memory,andseveraliterationsofdecodingarerunwithinthecoprocessorwithoutanyDSPintervention.

TheDSPsetsuptheEDMA3tosendthesystematicandparitydata,andtheinterleavertable(optional).

TheTCP2thenworksindependentlyoftheDSP.

12TMS320C6457Turbo-DecoderCoprocessor2SPRUGK1–March2009

SubmitDocumentationFeedback