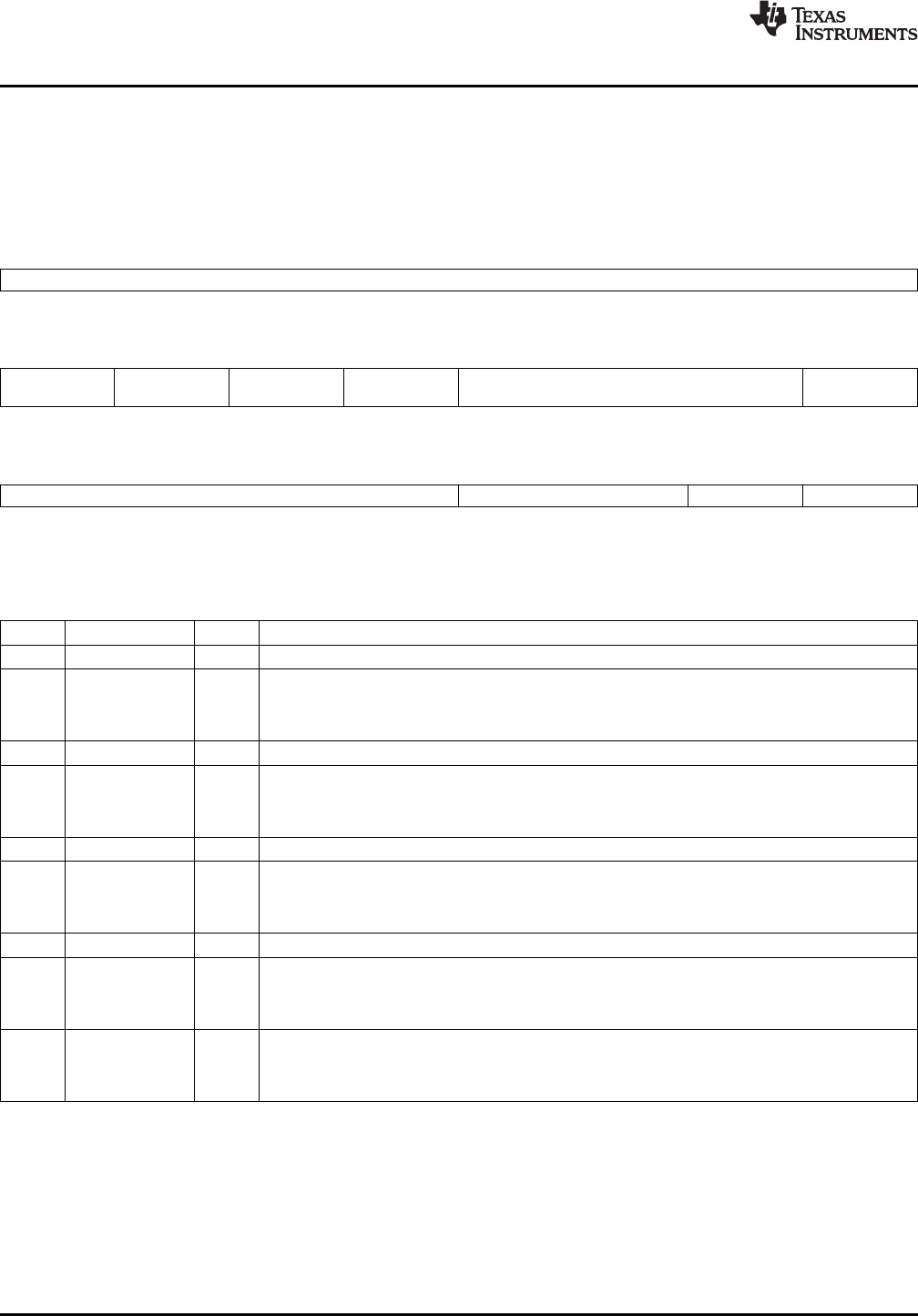

6.5TCP2InputConfigurationRegister3(TCPIC3)

Registers

www.ti.com

TheTCP2inputconfigurationregister3(TCPIC3)isshowninFigure36anddescribedinTable9.TCPIC3

informstheTCP2ontheEDMA3dataflowsegmentation.

Figure36.TCP2InputConfigurationRegister3(TCPIC3)

3116

Reserved

R/W-0

151413121198

OUTINPUT

ReservedReservedReservedMINITER

ORDERSIGN

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

743210

MINITERReservedEPROREDEXMASTR

R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table9.TCP2InputConfigurationRegister3(TCPIC3)

BitFieldValueDescription

31-15Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

14OUTORDEROutputbitordering.

0Outputbitorderingfrom0to31

1Outputbitorderingfrom31to0

13Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

12INPUTSIGNMultiplychannelinputdata.

0Multiplychannelinputdataby+1

1Multiplychannelinputdataby-1

11-9Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

8-4MINITER0-31Minimumnumberofiterationstobeexecuted

01

11-31

3-2Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

1EPROREDPrologreduction.

0Prologreductiondisabled

1Prologreductionenabled

0EXMASTRDisable/enableMaxLog-MAP.

0Maxstardisabled(enableMaxLog-MAP)

1Maxstarenabled(enablelogMAP)

TMS320C6457Turbo-DecoderCoprocessor2 30SPRUGK1–March2009

SubmitDocumentationFeedback