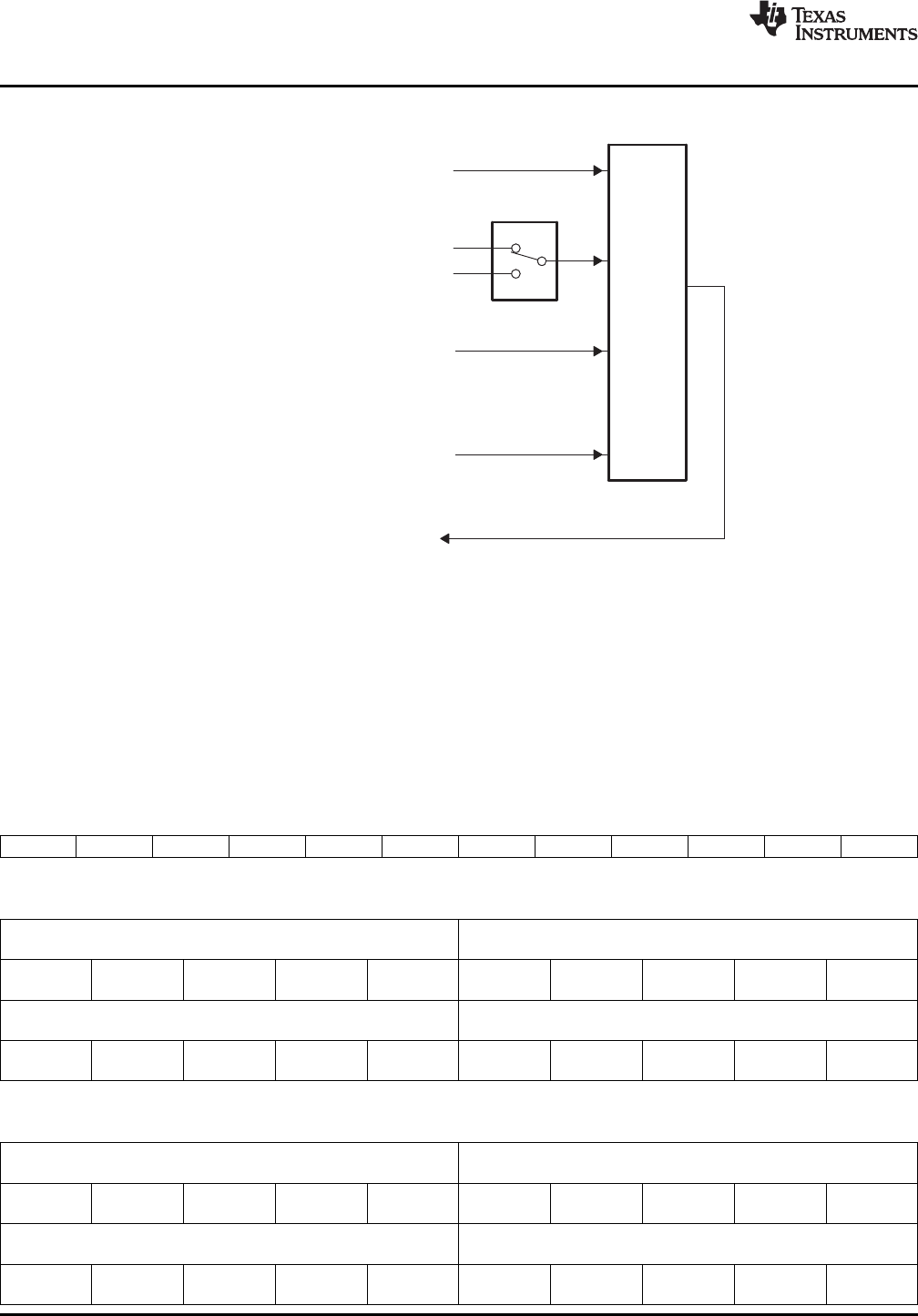

MAP

decoder

unit

MAP 1: Parity A or

MAP 2: Parity A’

MAP 2: Parity B’

MAP 1: Parity B or

Void input

MAP 1: Systemic or

MAP 2: Interleaved

(systematic)

MAP 1: De−interlaced (Apriori 2) or

MAP 2: Interleaved (Apriori 1)

MAP 1: Apriori 1 or

MAP 2: Apriori 2

Extrinsic saved as apriori

5.1InputDataFormat

5.1.1SystematicandParityData

Shared-Processing(SP)Mode

www.ti.com

Figure19.TCP2SharedProcessingBlockDiagram

TheoriginalsystematicandparitydataisorganizedasdescribedinSection4.1.1.TheDSPhastosplit

thedataforMAP0andMAP1asshowninthefollowingfigures.Thebaseaddressmustbedouble-word

aligned.Interleavedsystematicdata(X.)mustbecalculatedbytheDSPgiventheinterleavertable(see

Section4.1.2).Forbig-endianconfiguration,seeSection7.

Figure20.Systematic/ParityDataforRates1/2,1/3,1/4,1/5,and3/4

63:6261:5655:5049:4443:3837:3231:3029:2423:1817:1211:65:0

RSVDSP9SP8SP7SP6SP5RSVDSP4SP3SP2SP1SP0

Figure21.EN=1(Little-EndianMode)Rate=1/2

WordWord

N+1N

SP9SP8SP7SP6SP5SP4SP3SP3SP3SP0

0A1'00X10000X0

WordWord

N+3N+2

SP9SP8SP7SP6SP5SP4SP3SP3SP3SP0

0A3'00X30000X2

Figure22.EN=0(Big-EndianMode)Rate=1/2

WordWord

NN+1

SP4SP3SP2SP1SP0SP9SP8SP7SP6SP5

000A0X00A1'00X1

WordWord

N+2N+3

SP4SP3SP2SP1SP0SP9SP8SP7SP6SP5

000A2X20A3'00X3

TMS320C6457Turbo-DecoderCoprocessor2 22SPRUGK1–March2009

SubmitDocumentationFeedback