6.18TCP2InputConfigurationRegister15(TCPIC15)

www.ti.com

Registers

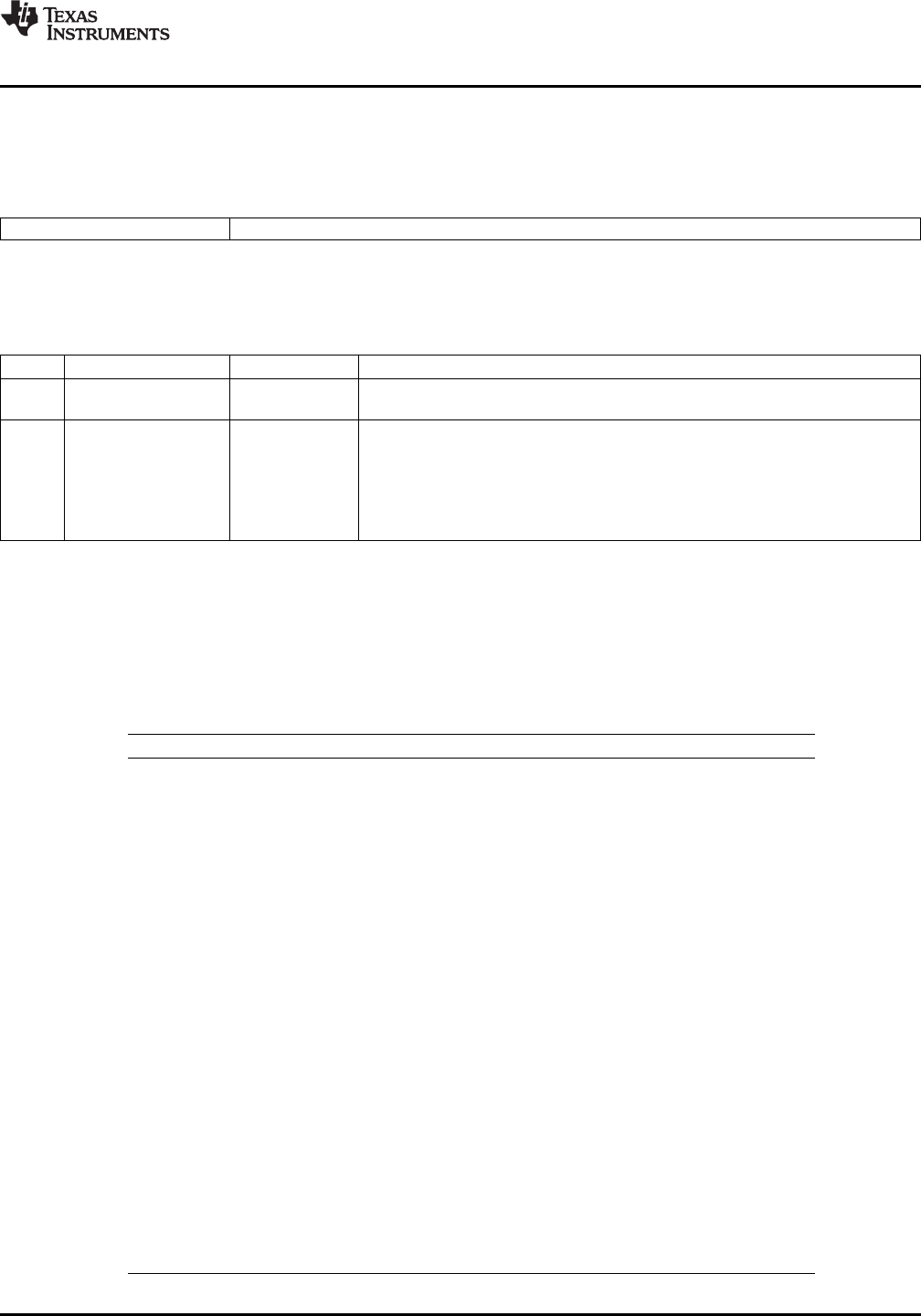

TheTCP2inputconfigurationregister15(TCPIC15)isshowninFigure48anddescribedinTable22.

Figure48.TCP2InputConfigurationRegister15(TCPIC15)

3124230

ReservedEXT_SCALE_12_15

R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table22.TCP2InputConfigurationRegister15(TCPIC15)FieldDescriptions

BitFieldValueDescription

31-24Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

23-0EXT_SCALE_12_150-FFFFFFFFhExtrinsicscalefactor

23:18Extrinsicscalefactor15

17:12Extrinsicscalefactor14

11:6Extrinsicscalefactor13

5:0Extrinsicscalefactor12

The16extrinsicscaleregistersare6bitseachandhavea(1,5)fixed-pointprecision.Theunsigned

fixed-pointnumberscanrangefrom0.0to1.0.Forexample,0.5isequalto0.10000or0x10.These

registersareonlyusedife_max_staris0.Ife_max_staris1,thentheextrinsicscalefactoris

automaticallysettoa1.0.Theresetvalueforeachregisteris1.0or0x20.

The16extrinsicscaleregistersareselecteddependingontheiterationnumberandactiveMAPasshown

inTable23.MAP0isthenon-interleavedMAPdecodeandMAP1istheinterleavedMAPdecode.

Table23.ExtrinsicScaleRegisters

IterationNumberMAPExtrinsicScalingRegister

000

011

102

113

204

215

306

317

408

419

5010

5111

6012

6113

7014

7115

8015

8115

...

...

...

31115

SPRUGK1–March2009TMS320C6457Turbo-DecoderCoprocessor241

SubmitDocumentationFeedback