6.6TCP2InputConfigurationRegister4(TCPIC4)

www.ti.com

Registers

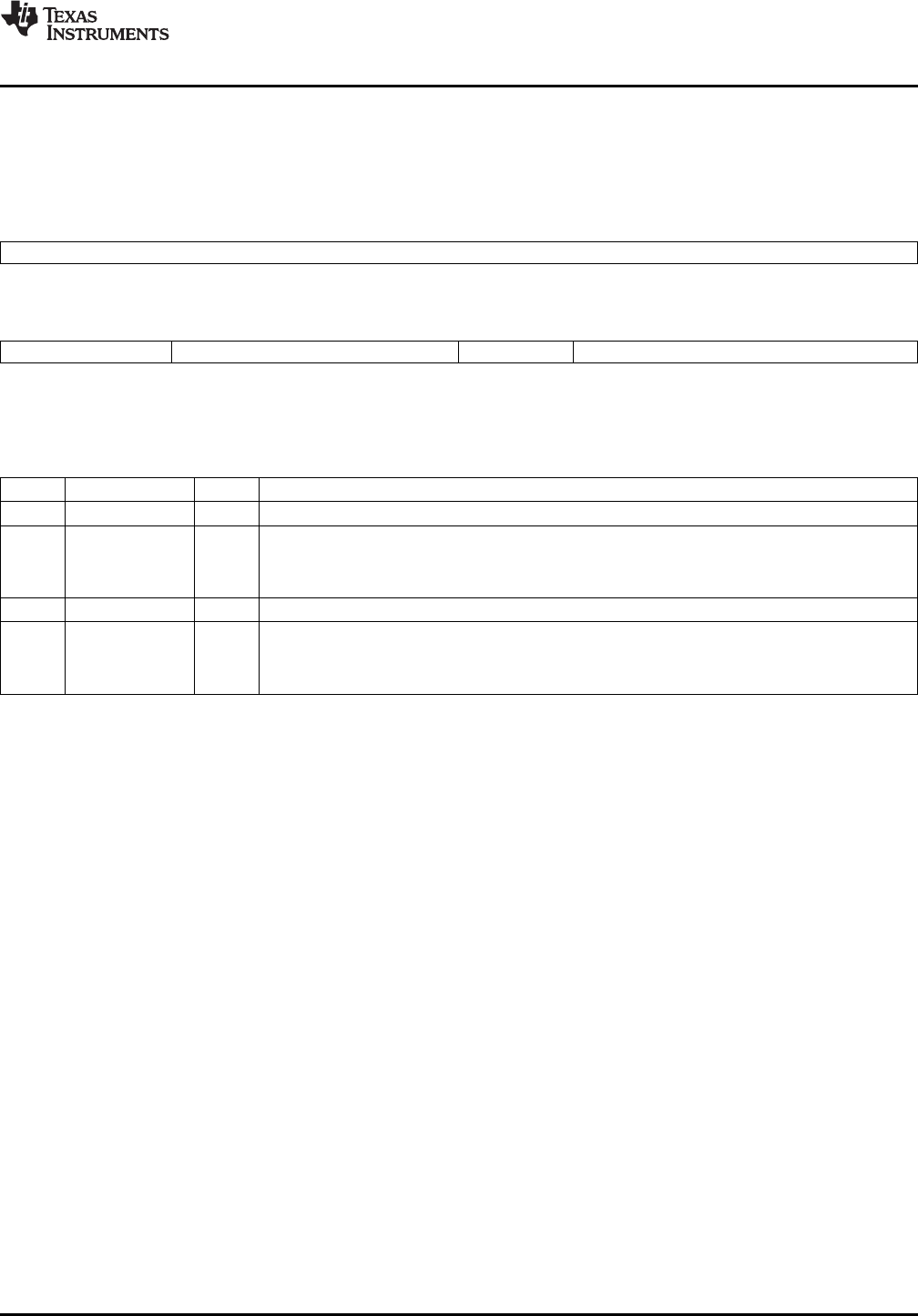

TheTCP2inputconfigurationregister4(TCPIC4)isshowninFigure37anddescribedinTable10.

TCPIC4informstheTCP2ontheEDMA3dataflowsegmentation.

Figure37.TCP2InputConfigurationRegister4(TCPIC4)

3116

Reserved

R/W-0

15131287650

ReservedCRCITERPASSReservedCRCLEN

R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table10.TCP2InputConfigurationRegister4(TCPIC4)FieldDescriptions

BitFieldValueDescription

31-13Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

12-8CRCITERPASS1-31NumberofconsecutiveCRCpassingiterationsrequiredbeforedecodertermination

01

11to31

7-6ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

5-0CRCLEN0-32CRCpolynomiallength

0DisableCRC

11to32=CRCpolynomiallength

SPRUGK1–March2009TMS320C6457Turbo-DecoderCoprocessor231

SubmitDocumentationFeedback