DM9161B

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver

9 Final

Version: DM9161B-12-DS-F01

January 31, 2008

39 DISMDIX I

(D)

HP Auto-MDIX Control

1: Disable auto mode

0: Enable HP Auto-MDIX mode

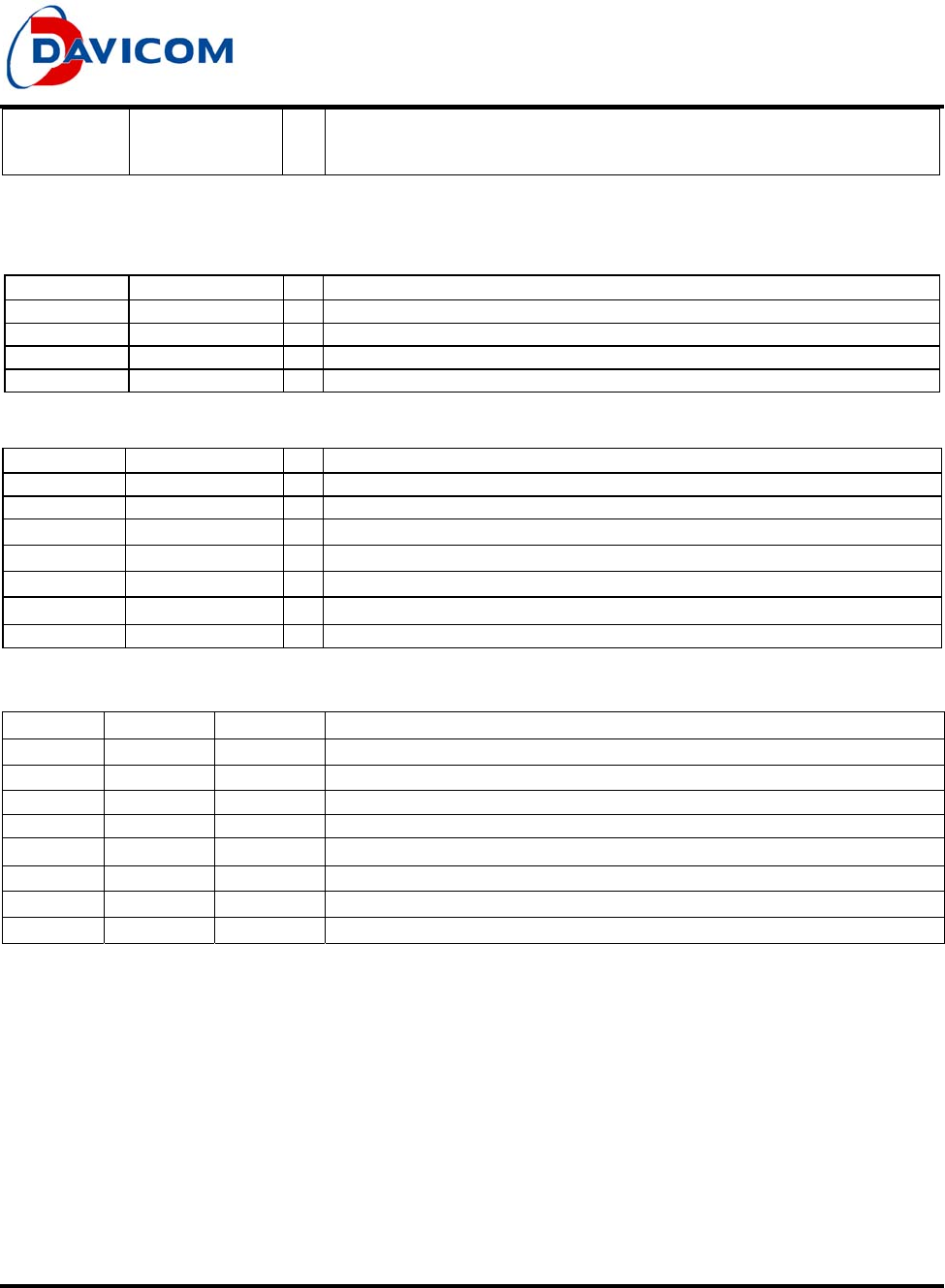

5.5 Bias and Clock, 4 pins

Pin No.

Pin Name

I/O

Description

47 BGRESG P Band gap Ground

48 BGRES O Band gap Voltage Reference Resistor 6.8K ohm +/- 1%

42 XT2 I/O Crystal Output or REF_CLK input for RMII mode

43 XT1 I Crystal Input or REF_CLK input for RMII mode

*RMII mode REF_CLK 50MHz choice XT1 or XT2.

5.6 Power, 12 pins

Pin No.

Pin Name

I/O

Description

1,2 AVDDR P 1.8V Analog Receive Power output

9 AVDDT P 1.8V Analog Transmit Power output

5 AGND P Analog Receive Ground

6 AGND P Analog Transmit Ground

46 AGND P Analog Substrate Ground

23,30,41 DVDD P 3.3V Digital Power

15,33,44 DGND P Digital Ground

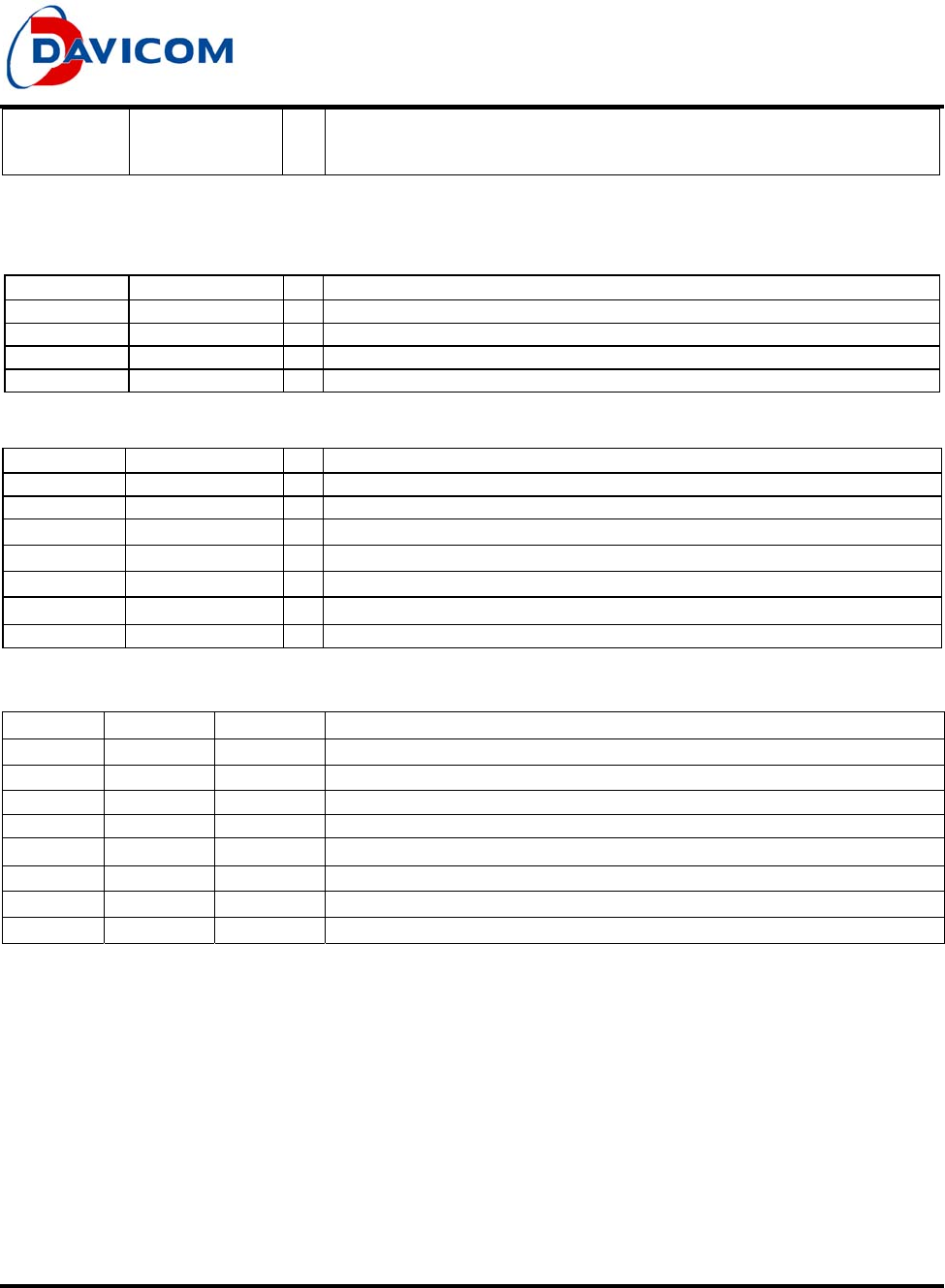

5.7 Table of Media Type Selection

OP2

OP1 OP0 Function

0

0 0 Dual Speed 100/10 HDX

0

0 1 Reserved

0 1 0 Reserved

0

1 1 Manually Select 10TX HDX

1

0 0

Manually Select 10TX FDX

1 0 1 Manually Select 100TX HDX

1

1 0

Manually Select 100TX FDX

1

1 1 Auto-negotiation Enables All Capabilities