DM9161B

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver

Final 34

Version: DM9161B-12-DS-F01

January 31, 2008

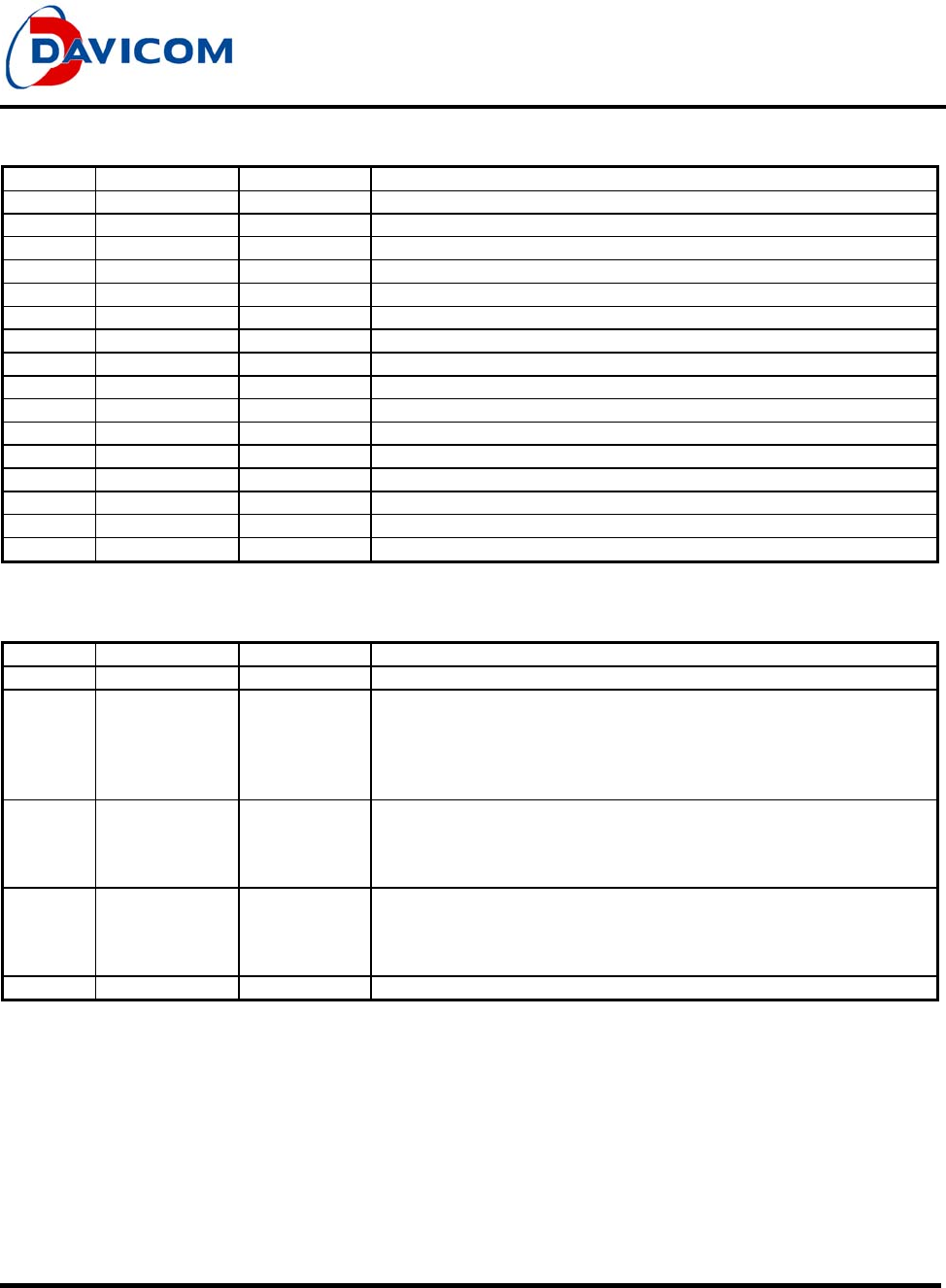

8.16 DAVICOM Hardware Reset Latch State Register (RLSR) – 24

Bit Bit Name Default Description

24.15 LH_LEDMODE 1,RO LEDMODE pin reset latch value

24.14 LH_MDINTR 1,RO MDINTR pin reset latch value

24.13 LH_CSTS 0,RO CABLESTS pin reset latch value

24.12 LH_ISO 0,RO TXCLK pin reset latch value

24.11 LH_RMII 0,RO COL pin reset latch value

24.10 LH_TP10SER 1,RO RXCLK pin reset latch value

24.9 LH_REPTR 0,RO RXER pin reset latch value

24.8 LH_TSTMOD 0,RO RXDV pin reset latch value

24.7 LH_OP2 1,RO LED2 pin reset latch value

24.6 LH_OP1 1,RO LED1 pin reset latch value

24.5 LH_OP0 1,RO LED0 pin reset latch value

24.4 LH_PH4 0,RO CRS pin reset latch value

24.3 LH_PH3 0,RO RXD3 pin reset latch value

24.2 LH_PH2 0,RO RXD2 pin reset latch value

24.1 LH_PH1 0,RO RXD1 pin reset latch value

24.0 LH_PH0 0,RO RXD0 pin reset latch value

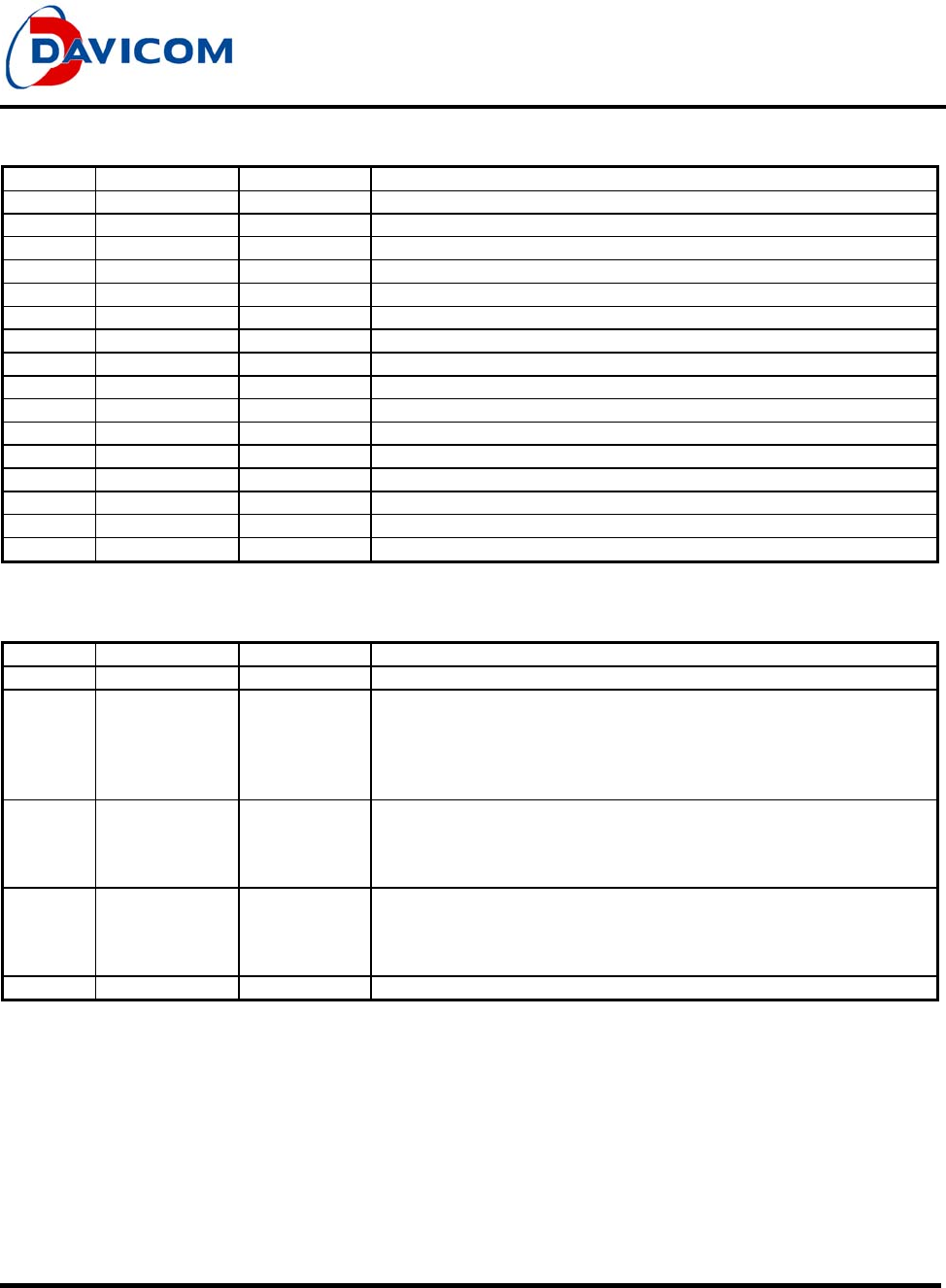

8.17 Power Saving Control Register (PSCR) – 29

Bit Bit Name Default Description

29.15-12 RESERVED 0,RO reserved

29.11 PREAMBLEX 0,RW Preamble Saving Control

When bit 10 of register 20 is cleared and bit 11 of

register 20 is set, the 10M TX preamble count is reduced.

1: 10-bit preamble bit is reduced.

0: 20-bit preamble bits is reduced.

29.10 AMPLITUDE 0,RW 10M TX Amplitude Control Disabled

1: disable TX amplitude reduce function

0: when cable is unconnected with link partner, the TX amplitude is

reduced for power saving.

29.9 TX_PWR 0.RW TX Power Saving Control Disabled

1: disable TX driving power saving function

0: when cable is unconnected with link partner, the driving current of

transmit is reduced for power saving.

29.8-0 RESERVED 0,RO reserved